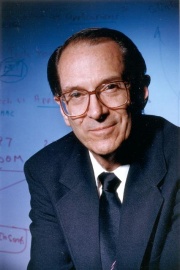

Bio/Description

Initiator of the first work in IBM on MOSFET memory, Terman was also involved in the program that led to the first IBM MOSFET memory product.

Born in San Francisco, his father was a professor at Stanford. During WWII, the family moved to the Boston area where he attended—first, public school and then transferred to a private school. After the war, in 1945 his father returned to Stanford and Terman attended public school in Palo Alto. After high school, he entered Stanford and received his B.S. degree in Physics in 1956, his M.S. degree in 1958, and his Ph.D. in 1961, both in Electrical Engineering.

He initially worked on measurement of high frequency characteristics of transistors, and then worked on silicon solar cells, publishing the first paper on solar cell spectral response. His Ph.D. thesis was the first work on the measurement of surface states using MOS capacitors. It is one of the most widely used measurements in the industry and resulted in a very widely referenced 1962 paper in Solid State Electronics, and the technique is now widely known as "the Terman Method."

In 1961 he joined IBM as a Research Staff Member where he worked on the design of a computer which directly implemented a high-level FORTRAN-like language directly in hardware. In 1963, he was promoted to Manager and oversaw a group that developed a magnetic film read only memory. In 1964 Terman initiated the first work in IBM on MOSFET memory and was involved in the program that led to the first IBM MOSFET memory product, for which he received the IBM Outstanding Contribution Award. He is the co-inventor of the Four-Transistor memory cell used in IBM and industry products and received the IBM Outstanding Invention Award and IBM Corporate Award.

During this time he also invented a method of stabilizing MOSFET device threshold voltage used in IBM products, receiving the IBM Outstanding Invention Award and IBM Corporate Award. Terman invented a high speed three-phase shift register used extensively in early IBM memory typewriters and received the IBM Outstanding Invention Award. His 1971 invited paper in the IEEE Proceedings on MOSFET memory circuits was widely referenced and is considered a classic paper.

From 1973 to 1979 he worked on MOSFET and CCD analog, logic, and memory circuits. He is a co-inventor and developer of the first MOSFET comparator with 1mV sensitivity. Terman also developed CCD multi-level storage memory and studied soft errors in memory systems. From 1979 to 1981, on temporary assignment, he served as a Member of the Technical Planning Staff, IBM Research Division, which involved monitoring progress and establishing directions and goals for the Division.

He has served as Manager, Second-line Manager, and Senior Manager from 1981 to 1991. During this period, Terman managed various groups of up to 25 to 30 people working on MOSFET and bipolar technology, circuits, and processor design. Achievements by these groups included: development of a 1 micron product MOS technology which formed the basis for the IBM 1 micron product technology; development of the high speed multiplier used in the IBM AS/6000 product line; design and development of high speed bipolar memories and logic circuits with industry leading performance; design of a series of S/370 architecture microprocessors which impacted IBM products; working with the product division on the IBM DRAM product technologies from 4Mb on, which are still in use by licensees of the IBM DRAM process.

Further achievements included the invention of the Substrate-Plate DRAM memory cell structure used in all IBM and IBM licensee 4Mb and beyond DRAM products and still widely used in the industry; design of a series of the world's fastest DRAMs, with performance 2–3X faster than conventional DRAMs, which impacted IBM DRAM products; and design of a series of NMOS and CMOS SRAMs with record-setting performance, culminating in a 1990 paper which received an ISSCC Outstanding Paper Award and which was used in IBM mainframe computer products. During this period, he received an IBM Outstanding Contribution Award for his work on what became the IBM 1 micron product CMOS technology, and an IBM Outstanding Invention Award and IBM Corporate Award as co-inventor of the Substrate-Plate DRAM memory cell.

From 1991 to 1993 he served as a Senior Member of the Research Division Technical Planning Staff, a temporary assignment dealing with the technical planning, directing, and goal setting for the Research Division. He has served as a Manager directing a group designing very high speed CMOS processors from 1993 to 1994. From 1994 to 2001 Terman served as a Program Manager for the design of CMOS high speed and low power systems. He has served as President of the IBM Academy of Technology from 2001 to 2003, and as Associate Director of the Systems Department, IBM Research Division from 2003 to 2006. He retired from IBM on January 31, 2006, after which he has served in a number of positions in IEEE, including President.

Citations:

-

Gender:

Male -

Noted For:

Initiated the first work in IBM on MOSFET memory and was involved in the program that led to the first IBM MOSFET memory product -

Category of Achievement: