- unknown (b.)

Bio/Description

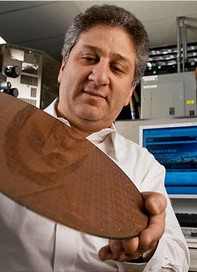

A 2006 IBM Fellow and Manager, BEOL Technology Strategy at the Thomas J. Watson Research Center, Yorktown Heights, NY; his work focus relates to CMOS on-chip Cu-based interconnection technologies, including low-k dielectrics, reliability physics, performance modeling and measurement, and evaluation of new materials and integration schemes. He is the Chief Architect and driving force behind IBM's copper chip wiring technologies, first announced in 1997. These were devised to increase the speed and reliability of modern integrated circuit chips while enabling their further miniaturization. More recently, he led IBM's change from glass to a novel low-dielectric insulator between the copper wires, for a further speed increase. These wires, about 1/1000 the size of a human hair, carry signals among the transistors on a silicon chip. A modern microprocessor, itself about the size of a thumbnail, contains over a mile of copper wiring. IBM has implemented this wiring in all its semiconductor products, including those that power its information technology systems. The global semiconductor industry has reoriented to follow the copper wiring architecture and roadmap which he defined. He is recognized as the leading expert in this field. On May 24, 2006 he was one of eight honorees to be named IBM Fellow -- the company's most prestigious technical honor. From 1990 to 2008, he authored or co-authored several publications just a few of which are: In 2007, ?Non-Poisoning Dual Damascene Patterning Scheme for Low-k and Ultra Low-k BEOL?, with W Cote, C Bunke, P Biolsi, W Wille, H Baks, R Conti, T Dalton, T Houghton, W Li Advanced Metallization Conference 2006 (AMC 2006), 2007; ?Optimization of silicon technology for the IBM System z9? with T Ivers, S Narasimha, TB Faure, JH Rankin, DA Grosch, MD Knox, M Khare, GB Bronner, HJ Nam, and others, IBM Journal of Research and Development 51(1-2), 5--18, Citeseer, 2007. In 2008, ?Interface engineering for high interfacial strength between SiCOH and porous SiCOH interconnect dielectrics and diffusion caps? with A Grill, M Lane, V Patel, S Gates, D Restaino, S Molis, Journal of Applied Physics103, 054104, 2008; and ?Performance and reliability of airgaps for advanced BEOL interconnects?, with S Nitta, S Ponoth, L Clevenger, X Liu, and T Standaert, Interconnect Technology Conference, 2008. IITC 2008. International, pp. 191-192. He also holds a 1997 patent for ?Diamond-like carbon for use in VLSI and ULSI interconnect systems?, with S A Cohen, A Grill, J R Paraszczak, and V V Patel, US Patent 5,674,355.

-

Gender:

Male -

Noted For:

Leading expert in the field of copper chip wiring technologies; wires, about 1/1000 the size of a human hair, carry signals among the transistors on a silicon chip -

Category of Achievement:

-

More Info: